# Sensor test of CMS ETL of MTD in USTC

Chengjun Yu, Nan Lu

University of Science and Technology of China

On behalf of CMS MTD group

2023.11.16

## Outline

- 1. Introduction of the MIP Timing Detector Project

- 2. Overview of the ETL

- 3. Test environment in USTC

- 4. Test result of single sensor and 15\*15 sensors

- 5. Layout of the new 16\*16 probe card and QC plan

- 6. Summary

## Introduction of the MTD Project

The CMS is going to introduce a new timing detector to measure timing of minimum ionizing particles (MIP) during the High Luminosity LHC (HL-LHC) era. The MIP Timing Detector (MTD) will reduce the effects of up to 200 pileup per bunch crossing, and thus, will provide better reconstruction of particles, and new capabilities for searches for the long-lived particles.

## Introduction of the MTD Project

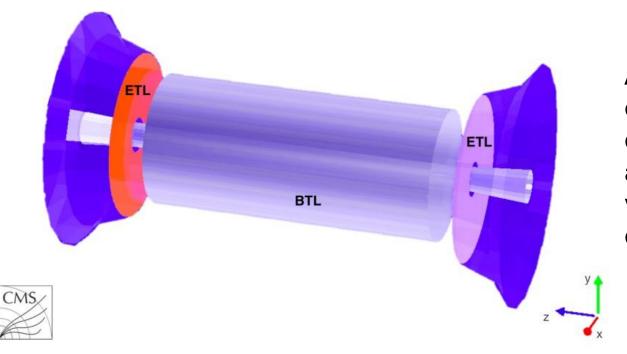

#### BTL: LYSO bars + SiPM readout:

- TK / ECAL interface: |n| < 1.45</li>

- Inner radius: 1148 mm (40 mm thick)

- Length: ±2.6 m along z

- · Surface ~38 m2; 332k channels

- Fluence at 4 ab-1: 2x10<sup>14</sup> n<sub>en</sub>/cm<sup>2</sup>

#### ETL: Si with internal gain (LGAD):

- On the CE nose: 1.6 < |η| < 3.0

- Radius: 315 < R < 1200 mm</li>

- Position in z: ±3.0 m (45 mm thick)

- Surface ~14 m<sup>2</sup>; ~8.5M channels

- Fluence at 4 ab<sup>-1</sup>: up to 2x10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup>

A schematic view of the GEANT geometry of the timing layers for simulation studies comprising a barrel layer (grey cylinder), and two silicon endcap (orange and light violet discs) timing layers in front of the endcap calorimeter.

# Overview of the ETL

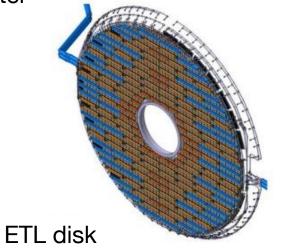

#### Coverage:

- $\geq$  z = 3 m from pp interaction

- $\triangleright$  0.315 m < R < 1.2 m

- ➤ Surface ~ 14 m2

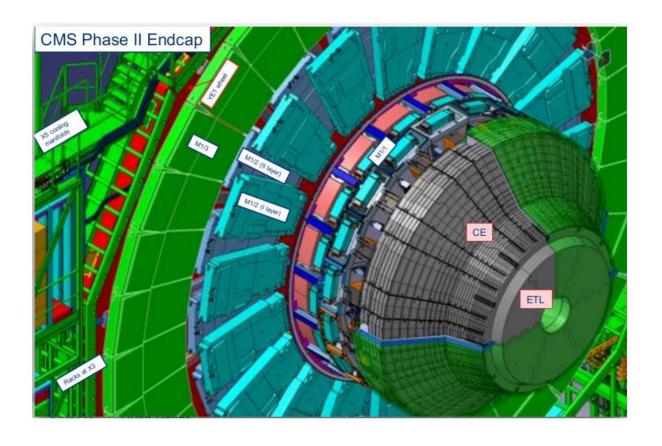

Endcap Timing Layer (ETL) will be mounted on the nose of the CMS CE calorimeter

# Overview of the ETL

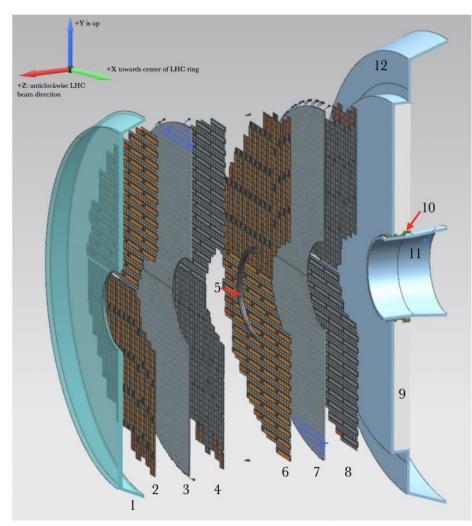

2 double-sided disks for each side

- double-sided disk → large geometrical acceptance

- 2 disks to achieve target time resolution:

- ➤ Single hit resolution < 50 ps

- > track resolution < 35 ps

- 1: ETL Thermal Screen

- 2: Disk 1, Face 1

- 3: Disk 1 Support Plate

- 4: Disk 1, Face 2

- 5: ETL Mounting Bracket

- 6: Disk 2, Face 1

- 7: Disk 2 Support Plate

- 8: Disk 2, Face 2

- 9: HGCal Neutron Moderator

- 10: ETL Support Cone

- 11: Support cone insulation

- 12: HGCal Thermal Screen

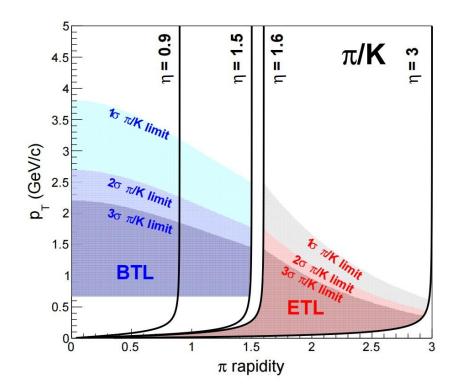

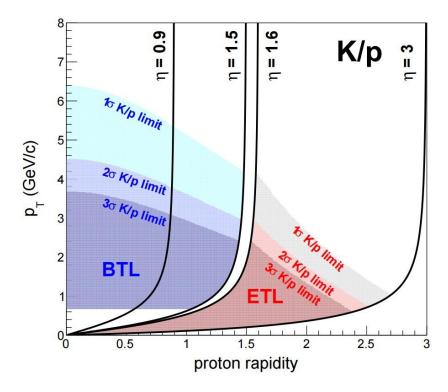

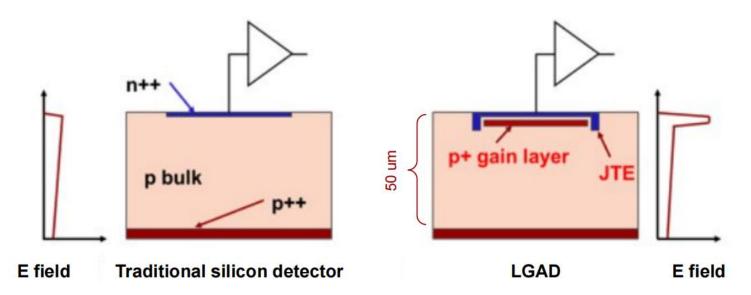

## LGAD sensors for ETL

- ETL will be instrumented with thin (50 um) silicon sensors based on the Low-Gain Avalanche Diode (LGAD) technology

- Thin sensor + LGAD technology → excellent timing performance

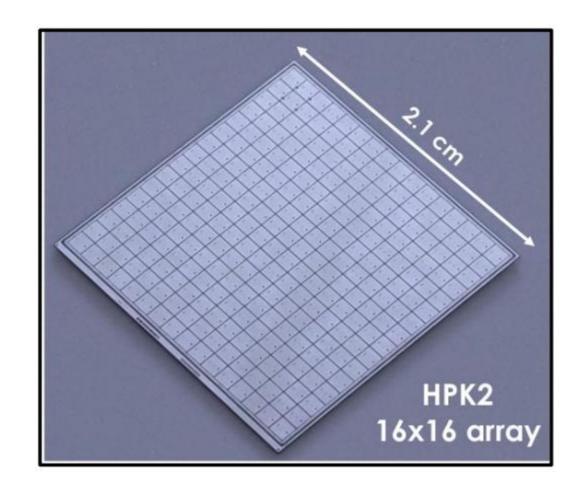

#### single

evolved during the past few years

16x16

## LGAD sensors for ETL

The final ETL sensor will be a 16x16 LGAD, to be bump-bonded to the ETL read-out chip (ETROC)

- 1.3 x 1.3 mm2 pads for a total surface of 21.4 x 21.6 mm2

- From the beginning to the end of HL-LHC lifetime, sensors are expected to:

- > achieve time resolution < 50 ps

- > deliver > 8 fC

ETL sensors need also to be radiation-hard to survive the harsh radiation environment @ HL-LHC → LGADs suited for this, as they proved to be able to withstand high radiation fluences

## LGAD sensors for ETL

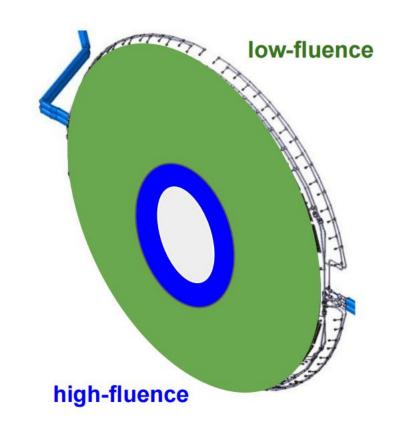

- Irradiation in ETL won't be uniform, but will have a radial dependence

- The fluence received by sensors at the end of the detector lifetime defines the so-called high- and low-fluence areas onto the disks:

- $\triangleright$  low-fluence area (  $\Phi \le$  1e15 neq/cm2), ~85% of the disk

- $\triangleright$  high-fluence (1e15 neq/cm2< Φ ≤ 1.5e15 neq/cm2), ~15% of the disk

- The 1e15 neq/cm2 threshold is set as it represents the turning point in terms of LGADs performance degradation

- ( Φ expressed in 1 MeV neutron equivalent)

# Test environment in USTC

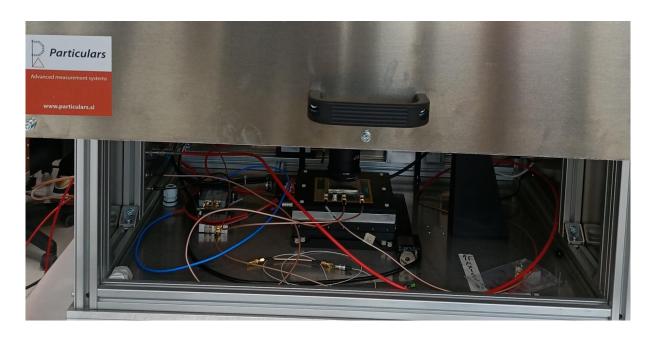

Scanning laser TCT (being assembled)

Environmental chamber: -70 ~ 180 degree

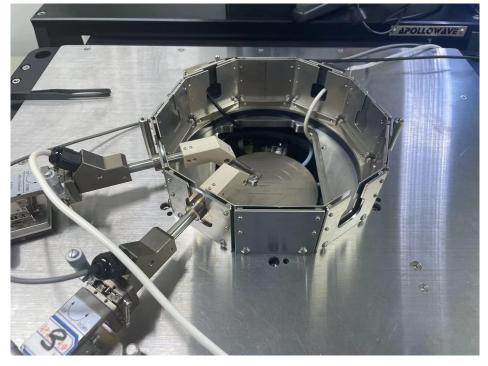

# Test environment in USTC

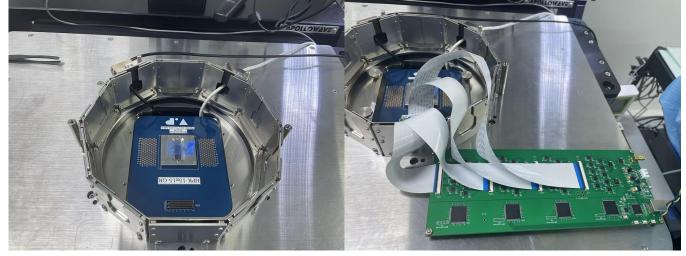

Probe station with up to 5 probes In clean room, Temperature adjustable

15\*15 probe card controlled by FPGA

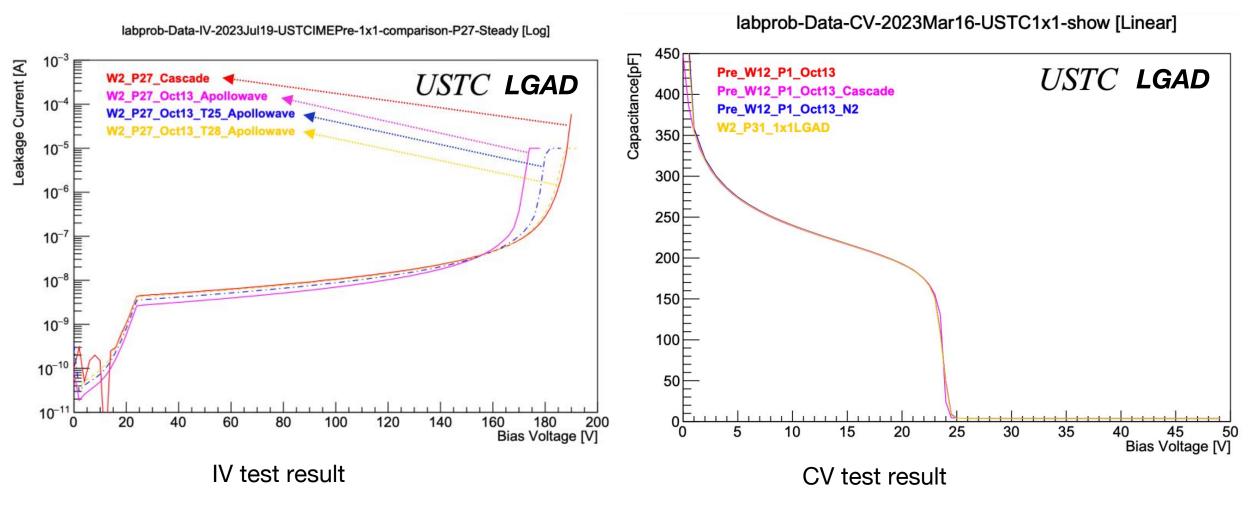

# Test result, 1\*1

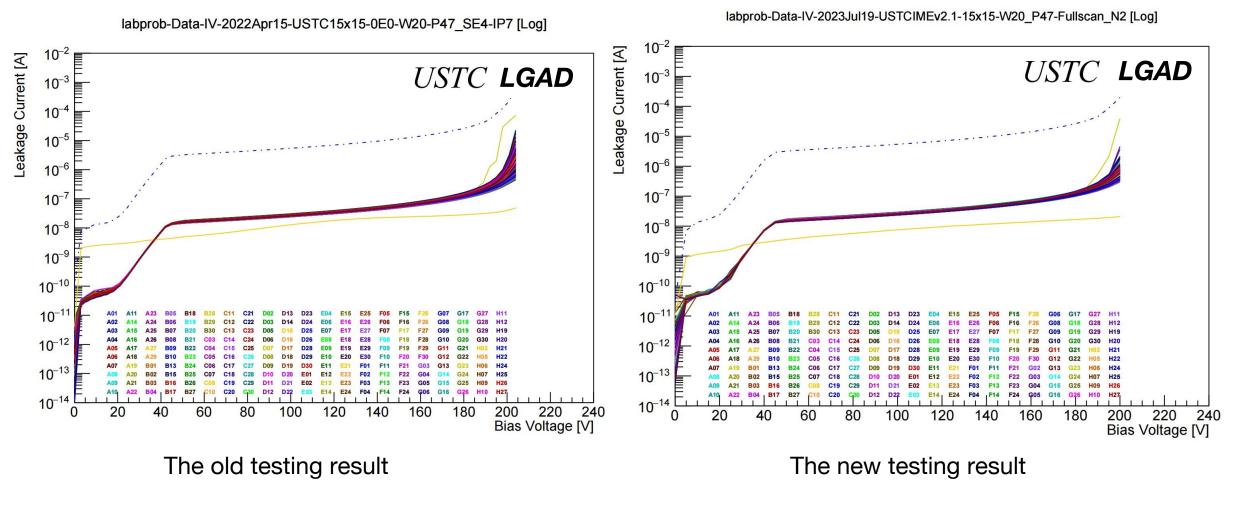

# Test result, 15\*15, IV

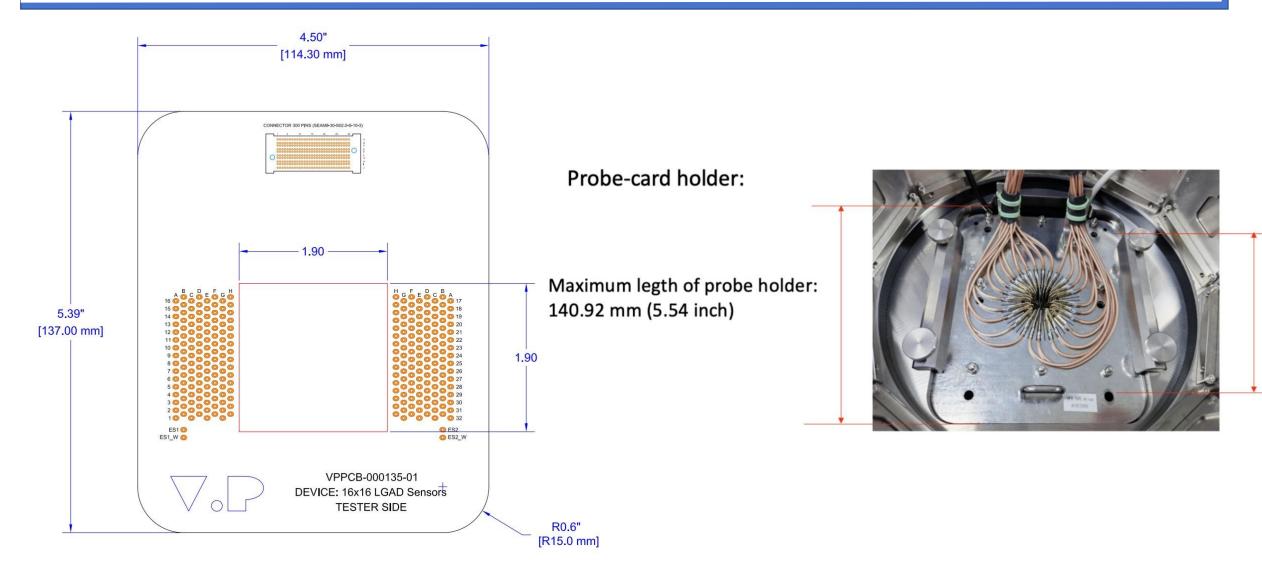

# Layout of the 16\*16 probe card

# Sensor QC plan

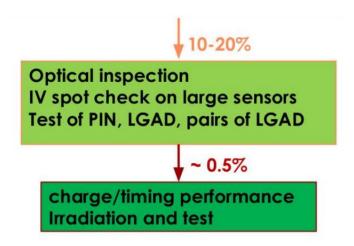

Quality control(QC) will start after quality assurance(QA) and post-wafer process

#### On 16x16 sensors:

- Optical inspection (chipping, scratches, other)

- Re-measure IVs cross-checking the vendor quality maps

- monitor current and breakdown voltage after processing

- spot "bad" pads not present on-wafer

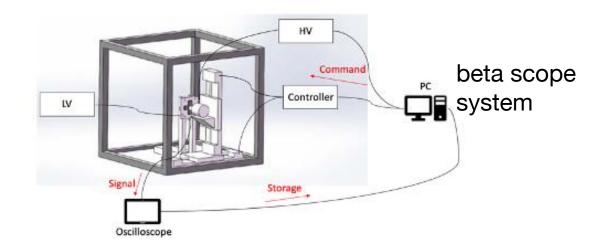

- measurements of timing performance (with beta setup) of pre-rad / irradiated samples

to be performed at ETL testing sites

# Summary

- The MTD project are progressing well. USTC will undertake sensor testing work.

- The repeated test result looks good. We are ready to test the new LGAD sensor.

- Radiation resistance testing will be conducted afterwards.

- After QA and post-wafer processing, the QC will start.