## **FOCAL-E Pixel Layer SystemC Simulation**

Jie Yi Jie.yi@cern.ch

# **Outline**

#### Introduction

- FOCAL-E Pixel Layer

- SystemC Framework

### Link Saturation

- Data rate per link

- Duration of Link Saturation

#### **Busy Violation** •

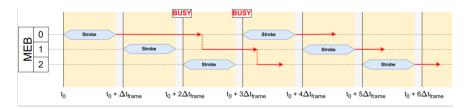

- ALPIDE Trigger and Strobe Scheme

Principles of Busy Violation

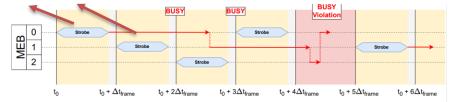

- Busy Violation rate per chip

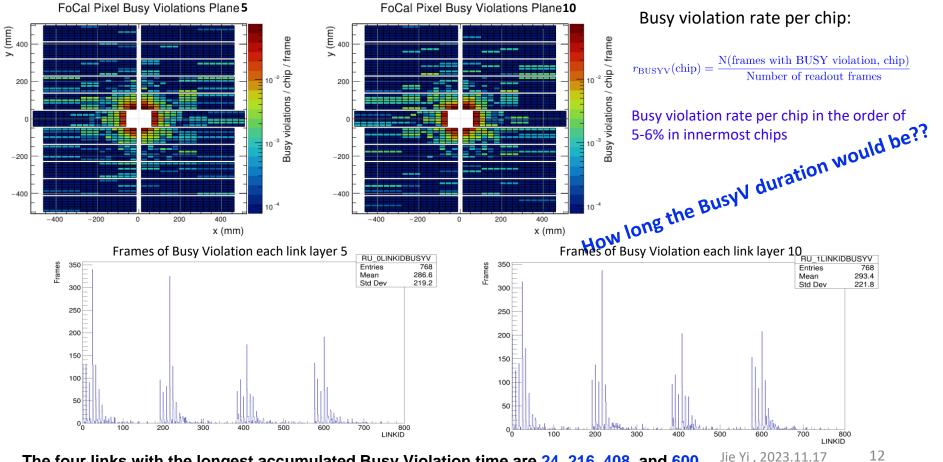

- Duration of Busy Violation

- Solution for Busy Violation

#### **Summary** •

# Introduction

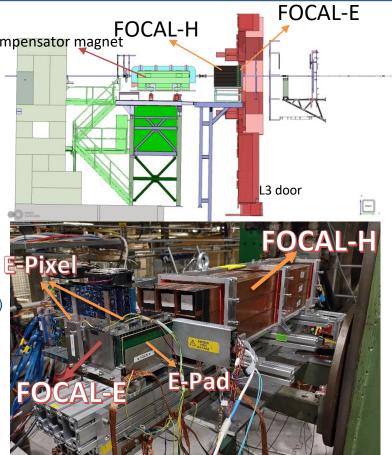

located 7m away from the IP(Interaction Point) ,slightly inside the Compensator magnet L3 door.

>>Should be located close to the beam, far from the interaction point(IP) >>The compensator magnet poses a upper limit to the furthest location from IP available for FoCal installation

$>>3.4 < \eta < 5.5$  over the full azimuthal coverage(pseudorapidity)

#### **Composed by three different** $\geq$ technologies

#### **Electromagnetic calorimeter**(Pad and pixels sensors) FOCAL-E PAD

- 18 layers of silicon pad sensors of 9 x 8 cm<sup>2</sup>

- Pad size 1 cm<sup>2</sup>

- Readout with HGCROC v2(High Granularity Calorimeter ReadOut Chip) **FOCAL-E Pixel**

- 2 ALPIDE pixel layers

- Monolithic active pixel sensors (MAPS) with pixel size of  $\sim$  30 x 30  $\mu$ m<sup>2</sup>

- Hadronic calorimeter(Copper/fibers) 9 Cu-scintillating fiber blocks Block size ~ 6.5 x 6.5 cm2

- Length ~110 cm

# **FOCAL-E Pixel Layer**

### FOCAL-E Model

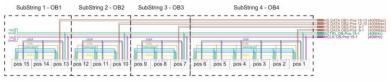

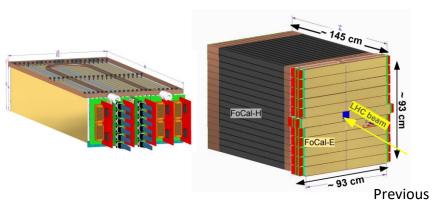

#### The FoCal-E is made of 20 layer

18 instrumented with Si-PAD and two (the 5<sup>th</sup> and the 10<sup>th</sup>) with Si-Pixel detectors

2 PAD&Pixel segments and 3 Pad segments form a module. Stacking  $2 \times 11$  of them makes the two half detectors

IB/OB 15-chip string

OB 15-chip string

#### IB/OB 12-chip string

Multi-chip strings Previous design:2 types the IB/OB 15-chip string the OB 15-chip string

Latest design:3 types(August 31, 2023) the IB/OB 15-chip string the OB 15-chip string the IB/OB 12-chip string

# **FOCAL-E Pixel Layer**

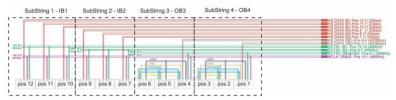

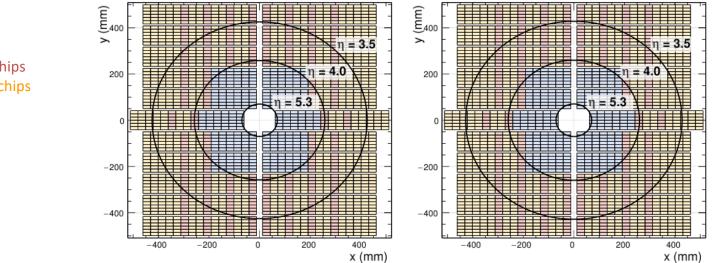

FoCal-E Pixel Layer 5 Simulation Chip Modes

FoCal-E Pixel Layer 10 Simulation Chip Modes

Blue: inner mode chips Red: outer mode master chips Yellow: outer mode slave chips

• Pixel layers at FoCal-E Layer 5 and 10

- The detector consists of 22 patches per layer each with 6 pixel strings.

- Each pixel string contains 15 ALPIDE chips

- 1980 ALPIDE(Alice Pixel Detector) chips per layer

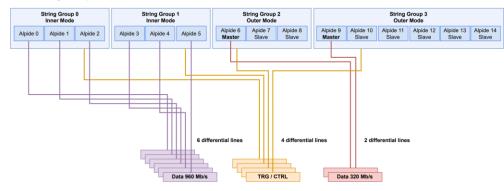

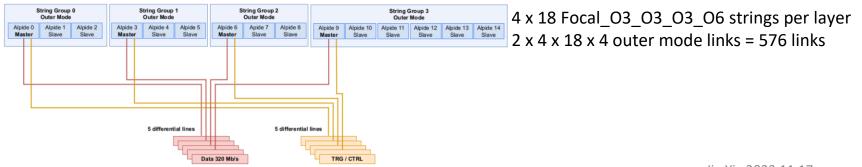

### String Models in Current SystemC model

#### Inner string, 15 alpides

4 x 15 Focal\_I3\_I3\_O3\_O6 strings per layer 2 x 4 x 15 x 6 inner mode links = 720 links 2 x 4 x 15 x 2 outer mode links = 240 links

#### Outer string, 15 alpides

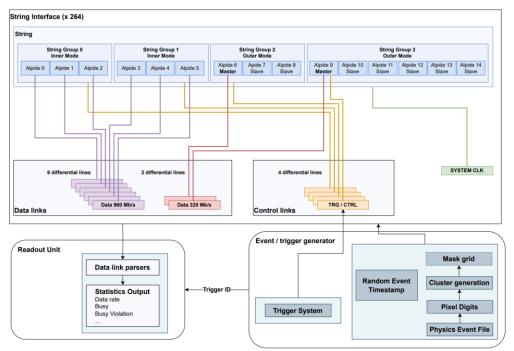

### SystemC Framework Basic Structure

Schematic overview on the functionalities of the FoCal-E Pixel Simulation Framework

- Input for the pixel hits : simulated minimum bias events(generated with the PYTHIA event generator and processed with FoCal simulation framework)

- The particle hits in the pixel layers are transformed to pixel hits in the chip internal coordinate system

- The **pixel cluster generation** model is applied for the formation of a realistic occupancy.

### Default

Mean cluster size  $n_{cl.size} = 4$ Mean cluster width  $\sigma_{cl.size} = 1.4$

The core of the framework is the digital simulation in SystemC of 264 pixel strings with 15 ALPIDEs each (here shown for an inner mode string).

# Link saturation

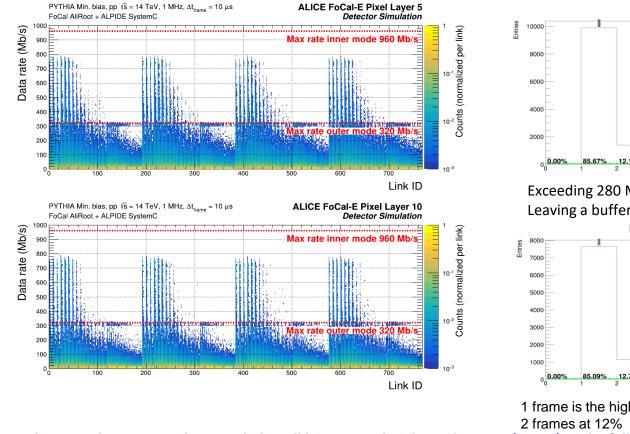

The inner data rate on the inner links will be operated with good margin (> 10%) to the full link speed Jie Yi , 2023.11.17 8 The outer mode links are simulated to run occasionally on full bandwidth of 320Mbps after having been hit by an high occupancy event.

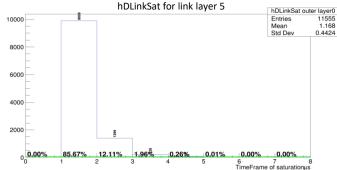

Exceeding 280 Mb/s is considered saturated links Leaving a buffer of 40 Mb/s between 280 Mb/s and 320 Mb/s

1 frame is the highest(approximately85%) 2 frames at 12%

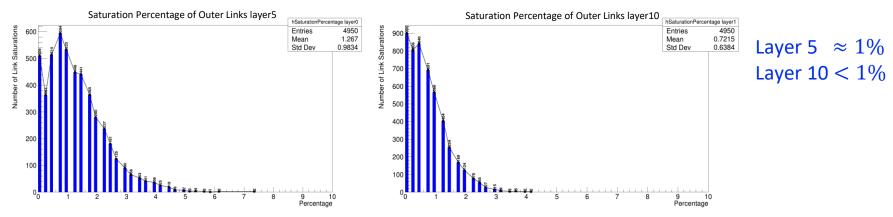

# Link saturation

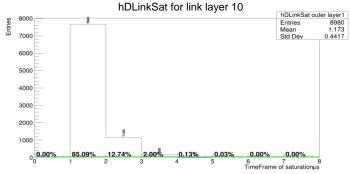

The proportion of saturated 3-group outer chips to the total outer chips:

### 3-group chips outer link saturation duration

#### 3-group chips are more prone to saturation Average duration of saturation is higher than that of 6-group chips

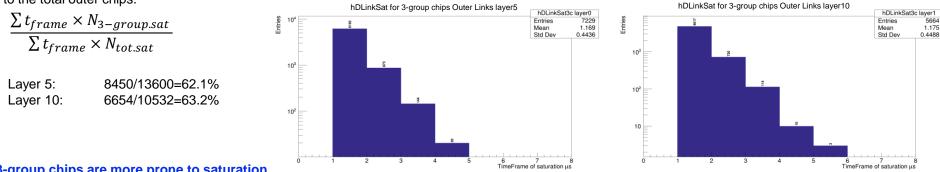

The percentage of saturated Outer links out of the total Outer links each time.

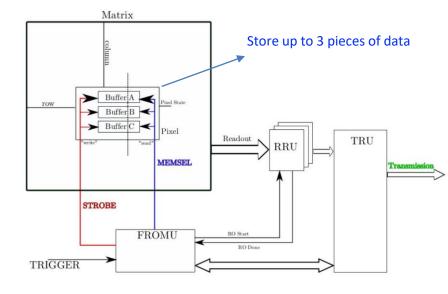

# **ALPIDE Trigger and Strobe Scheme**

Frame and ReadOut Management Unit(FROMU): controls the framing and readout in the chip keeps track of which buffers of the MEB are in use

#### Region Readout Unit (RRU):

readout of pixels from its region in the pixel matrix into a region FIFO

#### Top Readout Unit (TRU):

Readout from the FIFOs of the RRUs framing of the data

### **3-line global signal**

STROBE: latch a hit into the current Hit Storage Latch MEMSEL: read from the latches

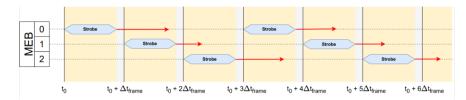

# **Busy Violation**

continuously triggered mode(Default)

$f_{trigger} = 100 \text{kHz}$  $\Delta t_{frame} = \frac{1}{f_{trigger}} = 10 \mu s$

- When the pixel is active during the opening of the strobe window, the pixel hit is latched into the Multi-Event Buffer (MEB) and remains there stored until the matrix readout of the event has started.

BUSYV happen in the pixel matrix / RRU and the "slow" pixel readout (50ns/pixel)

- High occupancy events

- Not dominated by data link speed

### When the trigger rate is faster than readout rate

### **Busy Flag:**

The pixel hits are being latched to the last free position in the MEB

### **Busy Violation:**

There is no free slot in the MEB left to latch the pixel hits The chip skips this trigger

The pixel hits are entirely lost for the newly requested time frame.

# **Busy Violation**

The four links with the longest accumulated Busy Violation time are 24, 216, 408, and 600

12

# **Busy Violation**

1400

1200

1000

800

600

400

200 0 L

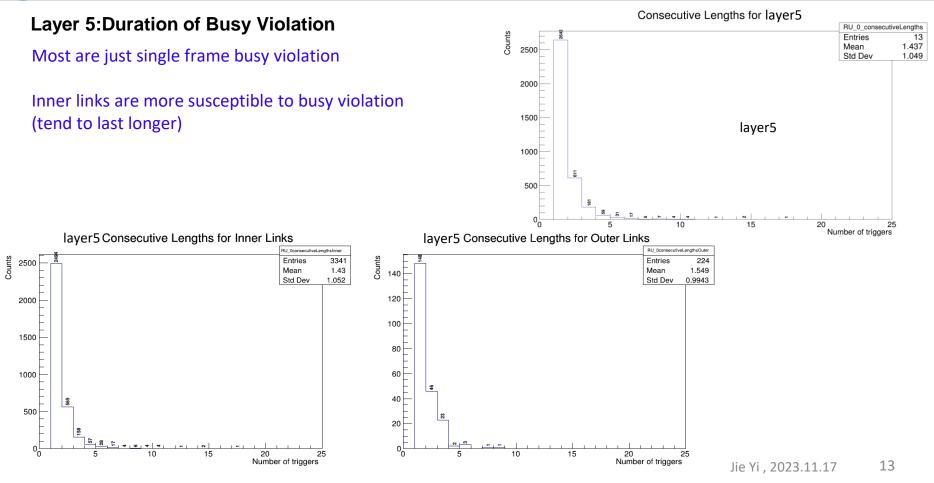

# **Busy Violation**

Counts

Mean

Std Dev

1.976

1.96

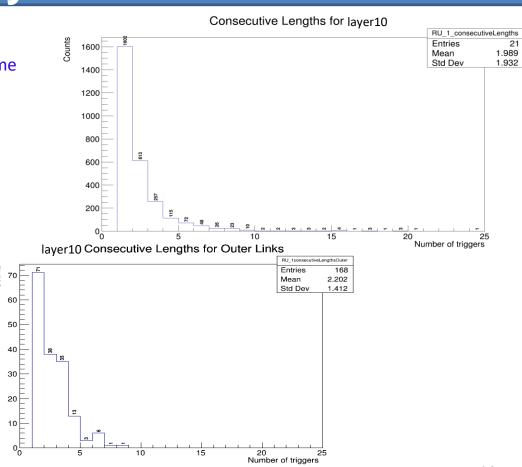

#### Layer 10: Duration of Busy Violation

Reduction in Busy Violations lasting just one frame

Increase in longer durations of Busy Violation

layer10 Consecutive Lengths for Inner Links RU 1consecutiveLengthsInner 1600 Counts Entries 2624

10

15

20

Number of triggers

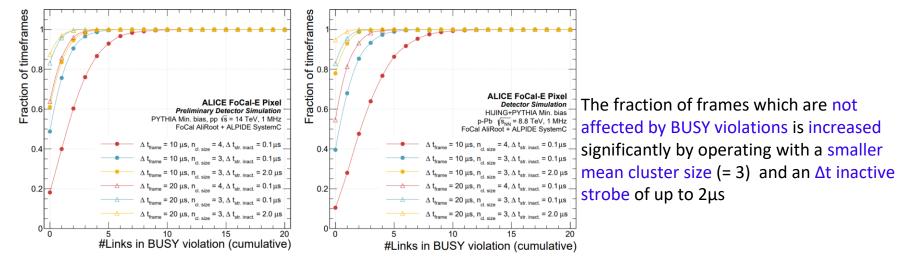

Various options are being studied:

- By back biasing the ALPIDEs, the average pixel cluster size can be reduced probably from 4 to 3, thus reducing the overall occupancy in the pixel by roughly a factor <sup>3</sup>/<sub>4</sub>

- Increasing the time frame length provides more time for the pixel matrix regions to be read out, and reduces the number of events which are being latched twice since less triggers are sent.

Fraction of frames with the cumulative number of links in BUSY violation

# Summary

- FoCal is part of the upgrade project of ALICE during Run 4 (starting from 2029)

- Link Saturation

-Inner link and outer link operate smoothly in most cases

-outer link have approximately a 1% probability of reaching link saturation

Busy Violation

-Inner links are more susceptible to busy violation and they tend to last longer

-Most are just one single frame of Busy Violation

-Pixel Layer 1(Layer 10) tends to have a longer duration of Busy Violation

• Solution for the Busy Violation

### Thanks for the attention!